By Dr. Shu-Jen Han, CTO, SEEQC

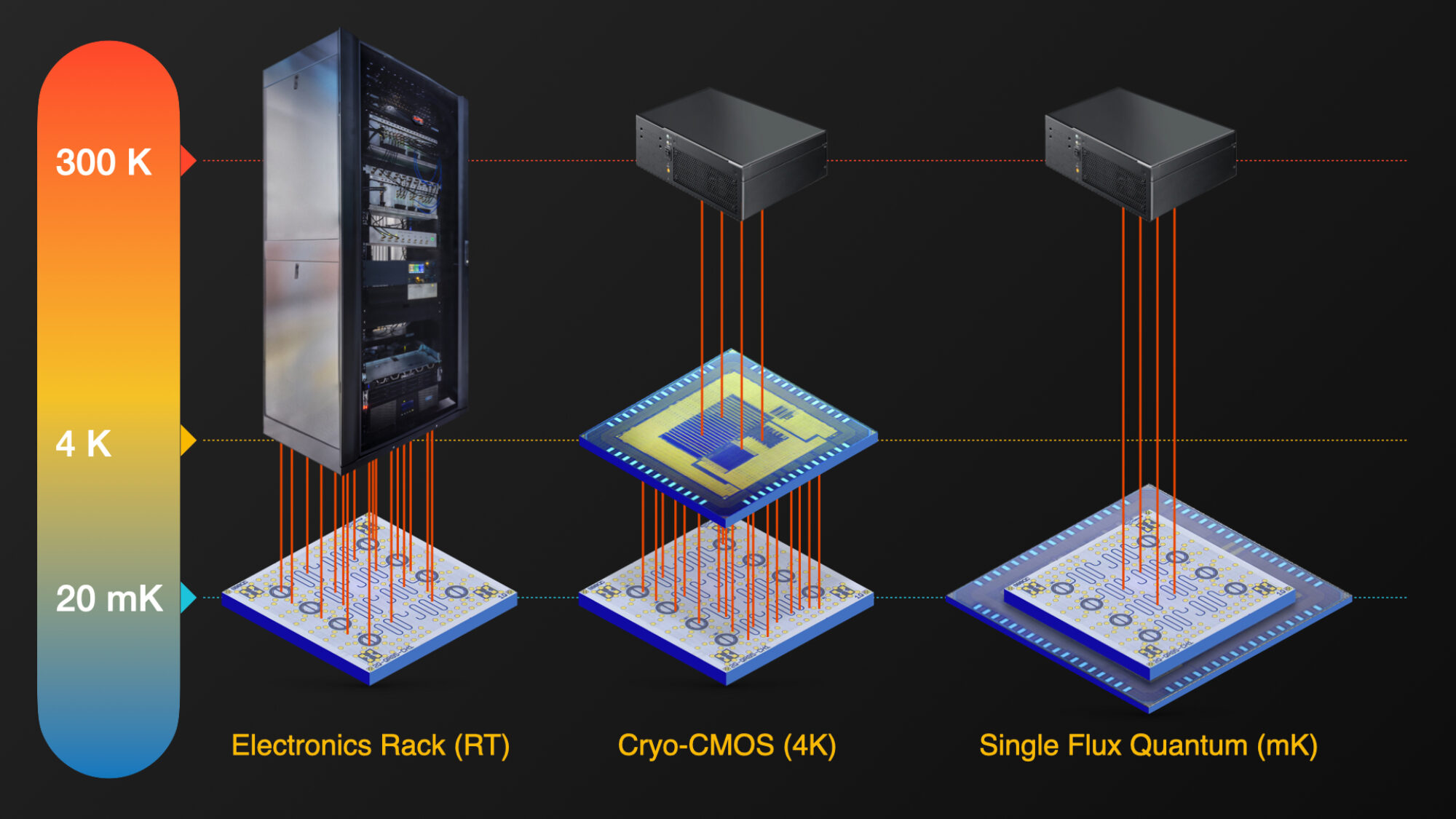

Today, researchers and engineers working in the field of superconducting based quantum computers agree that one of the biggest challenges of realizing a system beyond 1,000 – 10,000 qubits is the scalability of qubit control and readout electronics and associated wires and components. Current state-of-the-art quantum computers rely on racks of room temperature electronics to drive qubits sitting at the millikelvin stage, which is hardly scalable from the points of footprint and energy consumption. The integration level is just too low.

Highly integrated chip technology is the foundation of ever-increasing system performance and functionality in today’s CPU/GPU based computing platforms. Following this footstep in the microelectronic industry, quantum computing, to be scalable, needs to develop similar chip-based solutions by integrating key control and readout electronics directly with qubits on the same chip or through chip packaging technologies. However, the very limited cooling capacity at qubit operating temperature (10-20 mK) hindered the realization of this concept as any circuit implemented by conventional CMOS technology can easily heat up the system and destroy the qubit performance.

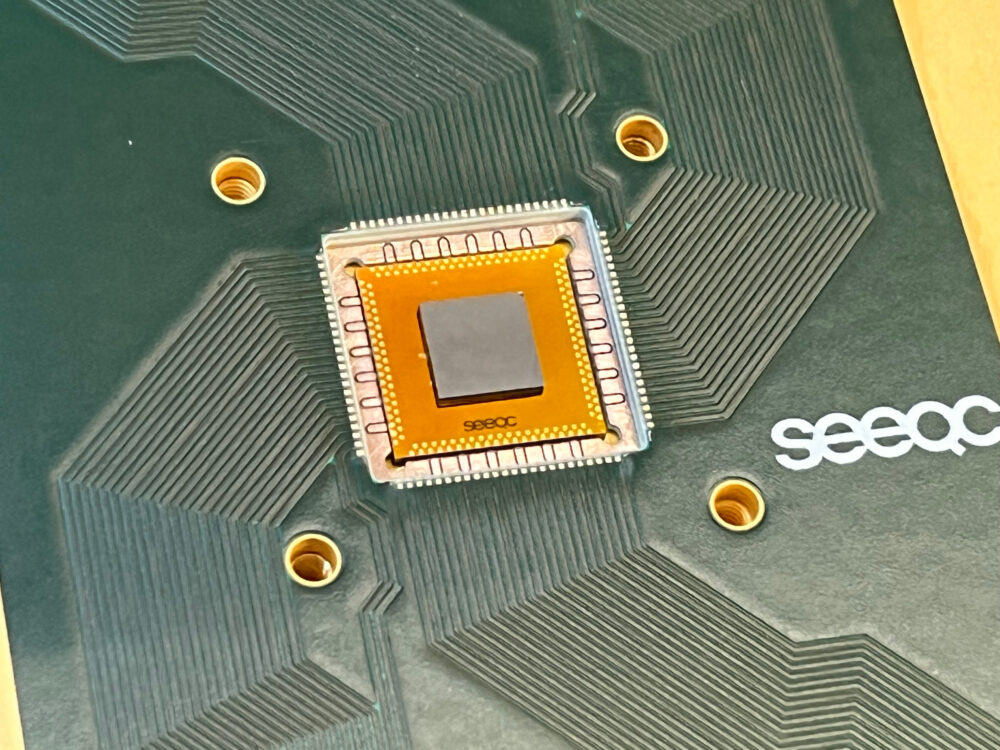

In this year’s APS March meeting, our team will showcase our chip solutions to address this quantum computer scaling issue. Instead of CMOS, we use Energy-efficient Rapid Single Flux Quantum (ERSFQ) logic technology which provides orders lower power consumption and enables the co-existence of qubits and control/readout circuitry. In addition, we developed a digital scheme (vs. conventional microwave scheme) that significantly simplifies the circuit complexity (thus lower power and smaller area). We will have three presentations covering all essential functions of operating a quantum computer:

1. High-Fidelity X/Y Control:

We will show how our technology enables high-fidelity qubit control with no observable quasiparticle poisoning

2. Two-Qubit Gate with Digital Flux Control:

Our approach to two-qubit gates, utilizing digital flux control, significantly reduces flux cross-talk

3. Compact On-Chip Digital Qubit Readout:

Leveraging our proprietary Josephson Digital Phase Detector (JDPD) technology, we present a compact, efficient solution for on-chip qubit readout

Additionally, we demonstrate in our recent article how some of these technologies integrate into a full-stack quantum computer, showcasing the potential for a new, scalable quantum architecture that can power the next generation of quantum computing systems.

I believe that, for scientists and technologists actively trying to solve quantum computer scaling issues, these works show a critical first step toward a true chip-based solution.